HOME > プレスリリース > 2016 > 半導体集積回路のシリコンに代わる 大面積ゲルマニウムウェハー作製技術の開発に成功

半導体集積回路のシリコンに代わる 大面積ゲルマニウムウェハー作製技術の開発に成功

東京都市大学総合研究所ナノエレクトロニクス研究センター(東京都世田谷区)の澤野憲太郎教授(応用物性・結晶工学)ら研究チームは、半導体集積回路のシリコンに代わる超低消費電力化も可能な絶縁膜上の大面積ゲルマニウムウェハーを作製する新技術の開発に成功しました。

本成果は6月7日より名古屋大学にて開催される国際会議International SiGe Technology and Device Meeting (ISTDM 2016)にて発表の予定です。

成果のポイント

●半導体集積回路(LSI)の超低消費電力化も可能とするシリコン(Si)に代わるゲルマニウム(Ge)基板、特に絶縁膜上のGeウェハー(Ge-on-Insulator:GOI)の開発に成功しました。

●300mm以上の大面積Geウェハーも実現可能とする、エッチングストップ層を利用した新しい作製技術を開発し、非常に薄くかつ膜厚均一性に優れた基板が完成しました。

●本手法では、Ge膜に結晶歪みを導入でき、コンピュータ内部の信号伝達を、電流から光に置き換えるために必須となる、発光機能を持つGe基板が実現されました。

概要

今日の高度情報化社会を支えるLSIはSiをベースに作られており、社会の発展にはこの分野の継続的な発展が不可欠となります。しかし今この微細化に限界が訪れると同時に、消費電力の増大が差し迫った課題となっています。

そんな中、次世代材料として、Siに似た結晶構造、電子構造を有するGeが期待を集めています。Geは材料特性においてSiよりも移動度(※1)が格段に高いことからLSIを高性能化できるのみならず、歪みによって発光することから集積回路内の光配線化を実現でき、高効率光デバイスの作製を可能とします。

しかし、実用化に向けたコスト削減に必須となる大面積ウェハーをGeで作ることは非常に難しく、これまでSi基板に匹敵する大面積で高品質のGe基板を作製する技術は開発されておりません。

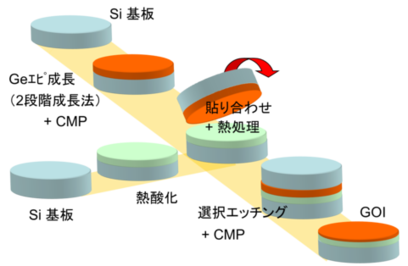

今回澤野教授らの研究チームが開発に成功したGeウェハー作製手法は、この大面積化、超高品質化を可能にする画期的なもので、具体的には高品質Ge薄膜をSi基板上に結晶成長(※2)させ、さらにこれを絶縁膜上に貼り合わせたうえで、選択エッチング(※3)によって上部層(Si基板)を取り除き、高品質GOIを作製するというものです(図1)。

図1 GOI作製方法

本手法の大きな特長は、まず高価なGe基板を一切使わないことにあり、GeのSi基板上への高品質結晶成長をキーテクノロジーとします。

特に2段階成長法を確立したことにより、4%の格子定数(※4)差による欠陥(※5)を後の工程で上側に位置させ、エッチングにより除去して完全に解消することができます。

また、結晶成長膜であるがゆえ、素子の特性向上に好都合な結晶歪み(※6)を持たせることができ、歪みを持ったGOIが形成可能となります。この歪みを有する膜は、発光素子やレーザー応用に有効なことから、集積回路内の光配線を実現可能にします。

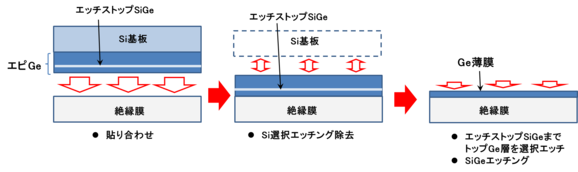

さらに本手法では、SiGeエッチングストップ層の導入により、エッチングによるGeの膜厚調整を結晶成長段階に設定でき、大面積ウェハーの全面で超薄膜かつ均一なGOIが実現可能です(図2)。

なお、電気測定により、このGOIはGe基板に匹敵する品質が確認されています。

図2 エッチングストップ層を利用した、

超薄膜GOIの作製手法

研究の背景

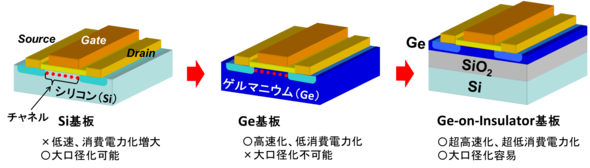

ICT(情報通信技術)は今日の社会において不可欠な技術ですが、それを根底で支えているのはSiによるLSIです。今後ますますの情報量増大に伴い、PCやスマホ、サーバーにおける消費電力は莫大となり、その抑制が世界的な喫緊の課題と言えます。これまで、素子サイズの縮小化によってLSIは高性能化、高集積化、低消費電力化を同時に達成してきたものの、近年、LSIの基本素子であるシリコン(Si)MOSFET(電界効果型トランジスタ、Metal Oxide Semiconductor Field Effect Transistor)(※7)の微細化には限界が訪れており、微細化によらない性能向上、電気配線の光配線への置き換え、等の技術革新が必須となっています。

その一つとして、デバイスのチャネルへの結晶歪みの導入が挙げられます。現在Siチャネルに結晶歪みを加えた、歪みSiチャネルが実用化され、これまでのSiチャネルを上回る移動度が実現されています。しかし、その移動度向上もわずかであり、性能向上の限界が訪れるのは時間の問題です。さらに、キャリアとして正孔(※8)を使うp型MOSFETの移動度は依然小さく、相補型MOS(CMOS)回路の高速化に向けて、正孔の移動度向上が強く求められています。また、低消費電力化のために、Si-on-Insulator (SOI)基板(※9)も利用されていますが、電子の移動度は材料で決まるため、ただのSi基板と変わらず、やはり問題となります。

そこで新規材料としてGeが注目されています。GeはSiと比べ、電子で2倍以上、正孔で4倍以上の移動度を有します。特に正孔については、他の半導体材料よりも大幅に高い移動度です。さらにGeでも、結晶歪みを加えることで、飛躍的に正孔移動度が増大することが確かめられています。すなわち、これまでのSiデバイスに代わりGeデバイスを実現すれば飛躍的なLSIの進展が望めます。さらにGeは、Si単体では不可能である発光素子応用が可能です。これは、歪みを導入したGeは、その電子構造が変化し、非常に発光しやすい材料に成り得るからです。つまりGe材料は、高速電子デバイスと同時に、高性能光デバイス実現にも有望です。

しかしGeの実用化で最も難しい点は、その基板の作製です。Ge基板はすでに市販されていますが、機械的強度はSiより弱く、Si基板のような大面積化は不可能です。大面積化はコスト削減に必須です。

Ge基板をSi絶縁膜上に貼り合わせるという手法を利用したGOIも作製されていますが、Ge基板を利用する点で大面積化が望めないだけでなく、貼り合わせ後にGeを薄膜化するため、大量の欠陥を導入する必要があるなど、量産型Si基板に匹敵する高品質化はいまだ達成されていません。

大面積化の唯一の方法は、大面積Si基板上へのGe薄膜の結晶成長です。しかし、SiとGeは格子定数が4%違うため、一般にはSi基板上に単結晶Geをきれいに無欠陥で形成することは困難です。

図3 各基板を利用したMOSFET

当研究成果が社会に与える影響、今後の予定

これまでの半導体技術の進展を継続することが可能となります。実際には、LSI内部のデバイスを、SiからGeへ替えるという大革新を起こすことになり、限界が迫るシリコン技術の壁を打ち破る技術と言えます。

電子デバイスの高速化と光配線の導入によって、消費電力量は一桁下がることが見込まれます。そのため、情報量の莫大な増加による消費電力の増加を抑制可能であり、今後10年から15年のエレクトロニクス技術、高度情報化社会のますますの継続的発展を可能にすることになります。

今後は数年以内に国内基板メーカとの大面積GOI基板共同開発、商品化を目指し、台湾など国外大手半導体メーカへの供給を狙っています。

さらに本技術は、プラスチックなどのフレキシブル基板上へもGe膜を形成できることになるので、フレキシブル基板上Ge光電子融合型デバイス(図4)を実現することで、各種センサー、ウェアラブルデバイスへの応用が期待でき、医療メーカ、ヘルスケアメーカなどターゲットを広げていく予定です。

図4 フレキシブル基板上Geデバイス

用語解説

※1 移動度:電子が電界によって動いているときの、速さと電界の比。移動度が高ければ、電界が一定ならば速さは早くなる。

※2 結晶成長:どこまでも周期的に原子が並んだ単結晶基板の上に、その原子配列を維持したまま新たに原子をくっつけていくこと。

※3 エッチング:SiやGe等の半導体基板を、各材料に適した化学溶液によって溶かし、基板を薄くすること。

※4 格子定数:SiやGe等の結晶の原子と原子の間の距離に相当する。GeはSiよりも原子の間隔が4%程度大きい。

※5 欠陥:SiやGe等の単結晶と呼ばれる半導体は、原子がジャングルジムのように完全に周期的に並んでいるが、その配列の乱れた部分を欠陥と呼ぶ。欠陥によってデバイス性能は大きく劣化する。

※6 結晶歪み:結晶の本来もつ格子の間隔(原子と原子の距離)が変わり、ある方向にだけ伸びたり縮んだりすること。

※7 MOSFET:LSIを構成する最も基本となる素子で、ゲートに印加する電圧によってオン・オフするスイッチング作用をしている。

※8 正孔: 励起された電子の抜け殻であり、プラスの電荷をもった粒子として扱える。正孔がチャネルを流れるMOSFETをp型MOSFETと呼ぶ。

※9 SOI基板:デバイスとなるSi薄膜が絶縁膜(埋め込み酸化膜、SiO2)の上に乗っている基板のこと。トランジスタの寄生容量を減らせるので、動作速度向上と消費電力削減に効果がある。

謝辞

本研究は、文部科学省 私立大学戦略的研究基盤形成支援事業『ゲルマニウムを基幹材料とするナノエレクトロニクス先端融合研究基盤の形成』(H27-H31)の一環として行われました。

【関連するリンク先】

~報道関係者からのお問い合わせ先~

●東京都市大学総合研究所 ナノエレクトロニクス研究センター 教授 澤野憲太郎

Tel: 03-5706-3111(代) E-mail: sawano@tcu.ac.jp

●学校法人五島育英会(東京都市大学グループ)法人本部広報室 高桜あゆみ

Tel: 03-3464-6916(直通)